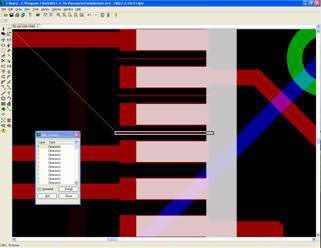

CommanderBob wrote:Is it normal for the little red line to appear between the pads? I understand that clicking delete does nothing. Can you see the red lines?

Greetings CommanderBob,

Only if the DRC finds a rule violation. Pads and traces can be placed anywhere, the DRC tool checks the placement against rules (clearance, drill size, trace angle, trace width, pad size and that all features are on grid, etc).

Changing to rules (or not running DRC) will avoid these errors. That also reduces the chance of the PCB being built correctly.

EAGLE flags the errors with an outline and cross-hatching, in the same colour as the layer. In this case the error is so small the outline has collapsed to a single line.

Clicking delete (in the DRC popup window) removes the current flag. Useful if the error has been fixed, or deliberately ignored. All DRC flags can be deleted at once.

Ideally, running DRC should generate "DRC:No errors". This is probably the most important step in the PCB design cycle!

Comments Welcome!

[/img]

[/img]